RISC-Ⅴ Architecture

6 Introduction to Assembly Language

6.1 Assembly Language

Assembly (also known as Assembly language, ASM): A low-level programming language where the program instructions match a particular architecture's operations.

Architecture: (also ISA: instruction set architecture) The parts of a processor design that one needs to understand for writing assembly/machine code.

Properties:

Splits a program into many small instructions that each do one single part of the process.

Each architecture will have a different set of operations that it supports (although there are similarities).

Assembly is not portable to other architectures.

Complex/Reduced Instruction Set Computing

Complex Instruction Set Computing (CISC)

Difficult to learn and comprehend language.

Less work for the compiler.

Complicated hardware runs more slowly.

Reduced Instruction Set Computing (RISC)

Simple (and smaller) instruction set makes it easier to build fast hardware.

Let software do the complicated operations by composing simpler ones.

Code:

op: operation name ("operator")dst: register getting result ("destination")src1: first register for operation ("source 1")src2: second register for operation ("source 2")

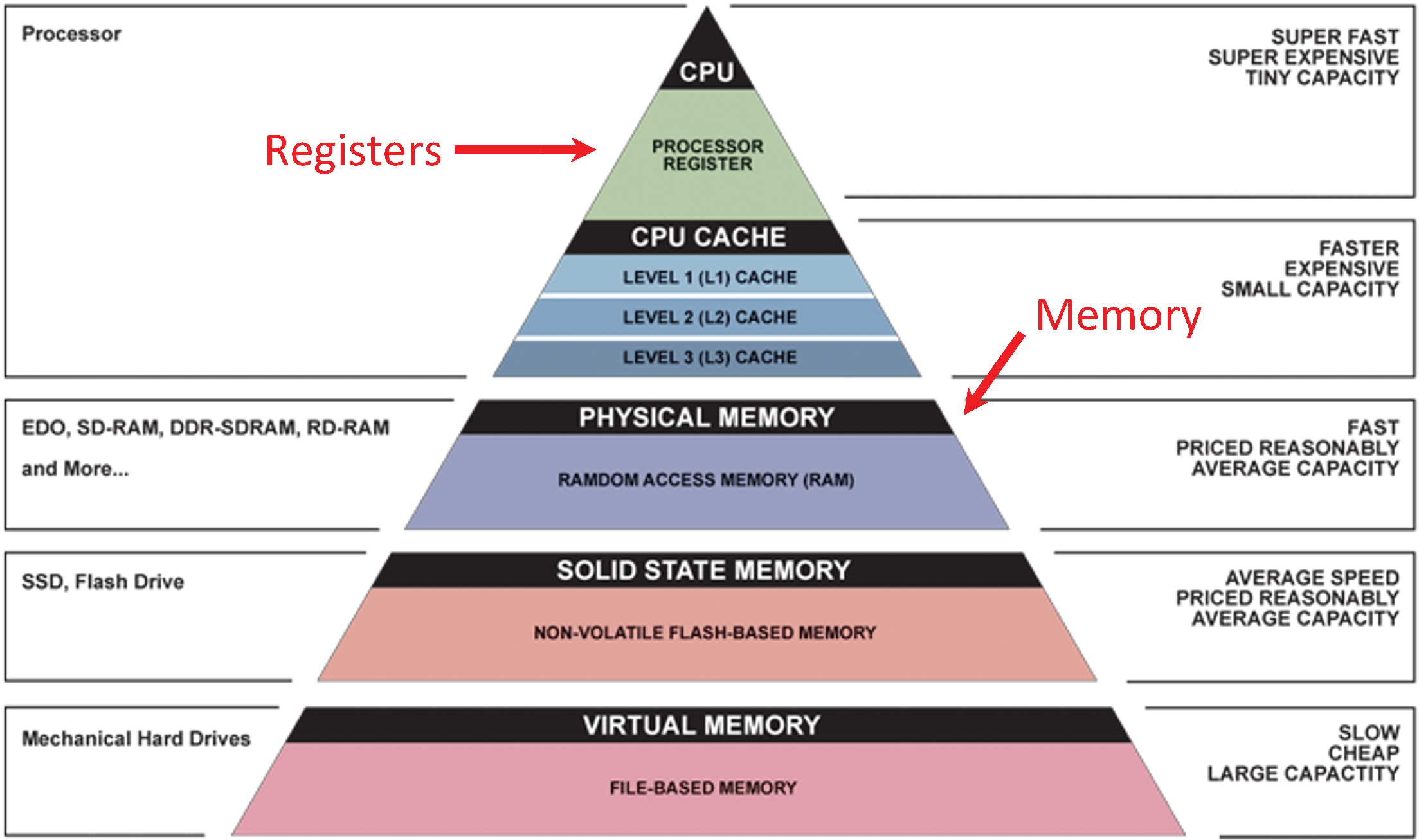

6.2 Registers

Assembly uses registers to store values. Registers are:

Small memories of a fixed size (in RV64, it is 64-bit wide).

Can be read or written.

Limited in number (in RV64, there are 32 registers), but very fast and low power to access.

Registers | Memory | |

|---|---|---|

Speed | Fast | Slow |

Size | Small e.g., 32 registers * 32 bit = 128 bytes | Big 4-32 GB |

Connection | More variables than registers? Keep most frequently used in registers and move the rest to memory | |

6.3 RISC-Ⅴ Instructions

In high-level languages, variable types determine operation.

In assembly, operation determines type, i.e., how register contents are treated.

Operations

6.3.1 Basic Arithmetic Instructions

Examples (Assuming here that the variables a, b and c are assigned to registers s1, s2 and s3, respectively)

Integer Addition

a = b + c;add s1, s2, s3Integer Subtraction

a = b - c;sub s1, s2, s3

6.3.2 Immediate Instructions

Immediates: Numerical constants.

Syntax:

Operation names end with "i", replace

source register with an immeidate. Immediates can up to 12 bits in size (-2048 to 2047, inclusive), and will be sign-extended to 64 bits before adding.

Example

6.3.3 Data Transfer Instructions

Specialized data transfer instructions move data between registers and memory.

Store: register to memory

Load: register FROM memory

Syntax:

memop: operation name (lw,sw, ...)reg: Register for operation source or destination.bAbbr: Register with pointer to memory ("base address")off: Address offset (immediate) in bytes ("offset")

Example

Load Doubleword

a = array[3];ld s1, 24(s2)Store Doubleword

array[10] = 3;sd s1, 80(s2)

6.3.4 Control Flow Instructions

Labels in RISC-Ⅴ: Defined by a text and followed by a colon (e.g., main:) and refers to the instructions that follows; generate control flow by jumping to labels.

Examples

Jump

Branch If Equal

if (i == j) { a = b; /* then */ } else { a = -b; /* else */ }beq s0, s1, then else: sub s2, x0, s3 j end then: add s2, s3, x0 end:Branch If Not Equal

if (i != j) { a = b; /* then */ } else { a = -b; /* else */ }bne s0, s1, then else: sub s2, x0, s3 j end then: add s2, s3, x0 end:Branch Less Than

if (i < j) { a = b; /* then */ } else { a = -b; /* else */ }blt s0, s1, then else: sub s2, x0, s3 j end then: add s2, s3, x0 end:Branch Greater Than or Equal (

bge)Branch Less Than Unsigned (

bltu, treat registers as unsigned integers)Branch Greater Than or Equal Unsigned (

bgeu)

Program Counter:

Program Counter (PC): A special register that contains the current address of the code that is being executed, and not accessible as a part of 32 registers.

Branches and Jumps change the flow of execution by modifying the PC.

Instructions are stored as data in memory (code section) and have addresses! Labels get converted to instruction addresses.

6.3.5 Shifting Instructions

Instructions Table

Logical Operations | C Operators | RISC-V Operators |

|---|---|---|

Bit-by-bit AND | & |

|

Bit-by-bit OR | | |

|

Bit-by-bit XOR | ^ |

|

Shift Left Logical | << |

|

Shift Left Logical Imm | << |

|

Shift Right Logical | >> |

|

Shift Right Logical Imm | >> |

|

Shift Right Arithmetic | >> |

|

Shift Right Arithmetic Imm | >> |

|

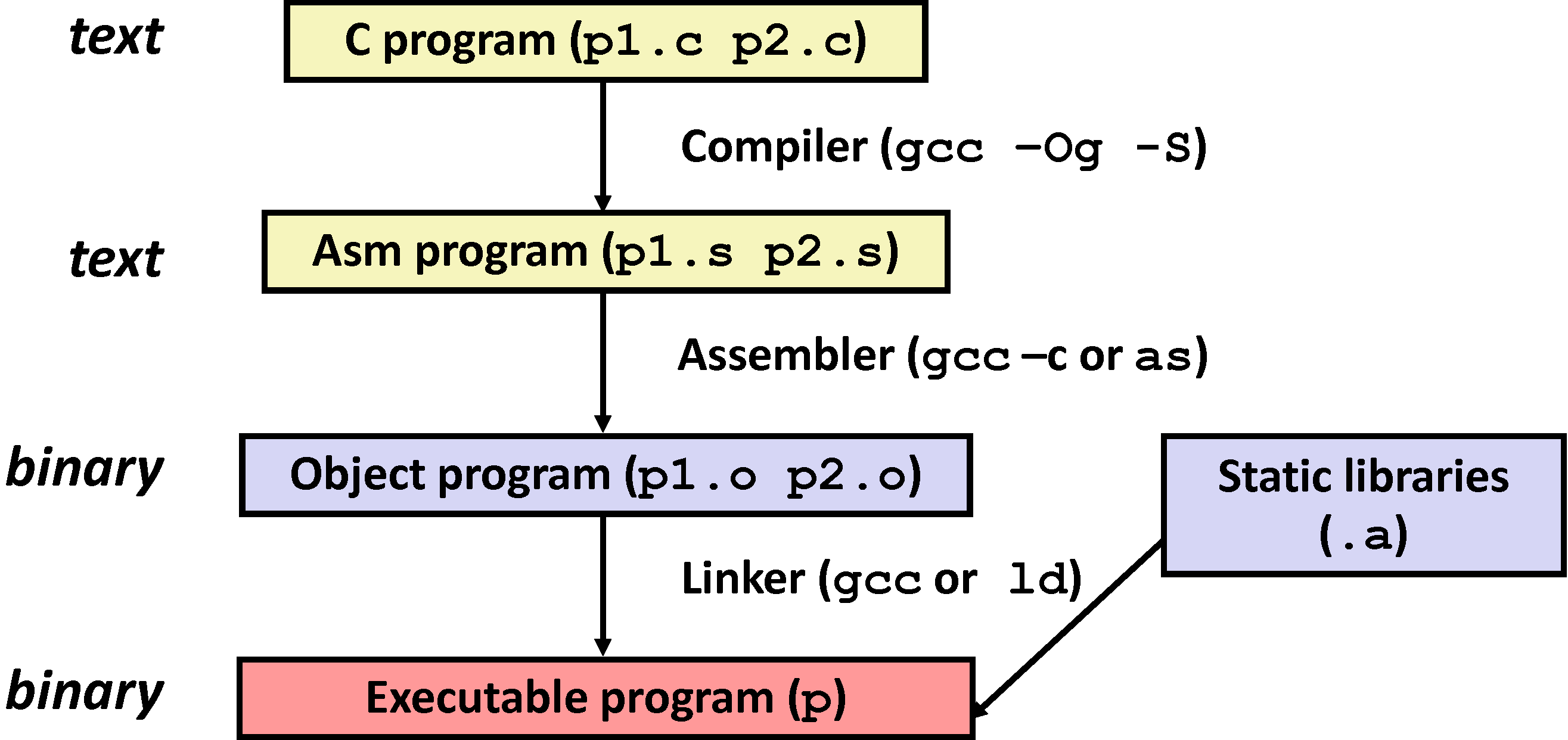

6.4 C, Assembly & Machine Code

Compile with the following code (debugging-friendly):

Use the following command to generate the assembly code:

Use the following command to disassembly the machine code: